Product Description

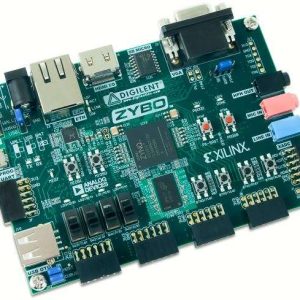

The Nexys 4 DDR is a drop-in replacement for our cellular RAM-based Nexys boards. Featuring the same Artix™-7 field programmable gate array (FPGA) from Xilinx®, the Nexys 4 DDR is a ready-to-use digital circuit development platform designed to bring additional industry applications into the classroom environment. The Artix-7 FPGA is optimized for high-performance logic, and offers more capacity, higher performance, and more resources than earlier designs. With its large, high-capacity FPGA (Xilinx part number XC7A100T-1CSG324C) and collection of USB, Ethernet, and other ports, the Nexys 4 DDR can host designs ranging from introductory combinational circuits to powerful embedded processors. Several built-in peripherals, including an accelerometer, a temperature sensor, MEMs digital microphone, speaker amplifier, and plenty of I/O devices allow the Nexys 4 DDR to be used for a wide range of designs without needing any other components. The most notable improvement is the replacement of the 16 MiB CellularRAM with a 128 MiB DDR2 SDRAM memory. Digilent will provide a VHDL reference module that wraps the complexity of a DDR2 controller and is backwards compatible with the asynchronous SRAM interface of the CellularRAM, with certain limitations.

The Nexys 4 DDR is compatible with Xilinx’s new high-performance Vivado® Design Suite as well as the ISE® toolset, which includes ChipScope™ and EDK. Xilinx offers free WebPACK™ versions of these tool sets, so designs can be implemented at no additional cost.

Support Materials

Datasheet (PDF)Schematics (PDF)

For all other material:

Stats:

Processor/IC: Xilinx Artix-7 FPGA XC7A100T-1CSG324C

Connector(s):

-

UART/JTAG USB port

-

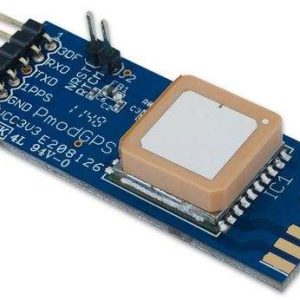

Pmod port for XADC signals

-

Audio connector

-

Ethernet connector

-

USB host connector

-

microSD card connector

-

12-bit VGA output

-

Four Pmod ports

-

Power jack

-

Programming: Vivado Design Suite as well as the ISE toolset

Features:

-

Xilinx Artix-7 FPGA XC7A100T-1CSG324C

-

15,850 logic slices, each with four 6-input LUTs and 8 flip-flops

-

4,860 Kbits of fast block RAM

-

Six clock management tiles, each with phase-locked loop (PLL)

-

240 DSP slices

-

Internal clock speeds exceeding 450 MHz

-

On-chip analog-to-digital converter (XADC)

-

128 MiB DDR2

-

Serial Flash

-

Digilent USB-JTAG port for FPGA programming and communication

-

microSD card connector

-

Ships with rugged plastic case and USB cable

-

USB-UART Bridge

-

10/100 Ethernet PHY

-

PWM audio output

-

3-axis accelerometer

-

16 user switches

-

16 user LEDs

-

Two tri-color LEDs

-

PDM microphone

-

Temperature sensor

-

Two 4-digit 7-segment displays

-

USB HID Host for mice, keyboards and memory sticks

-

Pmod for XADC signals

-

12-bit VGA output

-

Four Pmod ports