The Joint Test Action Group (JTAG)-HS2 programming cable is a high-speed programming solution for Xilinx field-programmable gate arrays (FPGAs). The cable is fully compatible will all Xilinx tools and can be seamlessly driven from iMPACT, Chipscope, and EDK. The HS2 attaches to target boards using Digilent’s 6-pin, 100-mil spaced programming header or Xilinx’s 2×7, 2mm connector and the included adaptor.

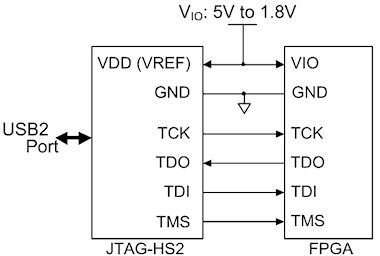

The PC powers the JTAG-HS2 through the USB port and will recognize it as a Digilent programming cable when connected to a PC, even if the cable is not attached to the target board. The HS2 has a separate Vdd pin to supply the JTAG signal buffers. The high speed 24mA three-state buffers allow target boards to drive the HS2 with signal voltages from 1.8V to 5V and bus speeds of up to 30MBit/sec. (See figure 1) To function correctly the HS2’s Vdd pin must be tied to the same voltage supply that drives the JTAG port on the FPGA.

The JTAG bus can be shared with other devices as systems hold JTAG signals at high-impedance except when actively driven during programming. The HS2 comes included with a standard Type-A to Micro-USB cable that attaches to the end of the module opposite the system board connector. The system board connector should hold the small and light HS2 firmly in place.

- Small, complete, all-in-one JTAG programming solution for Xilinx FPGAs

- Compatible with all Xilinx tools

- Compatible with IEEE 1149.7-2009 Class T0 – Class T4 (includes 2-Wire JTAG)

- Separate Vref drives JTAG/SPI signal voltages; Vref can be any voltage between 1.8V and 5V.

- High-Speed USB2 port that can drive JTAG/SPI bus at up to 30Mbit/sec

- JTAG/SPI frequency settable by user

- Uses micro-AB USB2 connector

- SPI programming solution (modes 0 and 2 up to 30Mbit/sec, modes 1 and 3 up to 2Mbit/sec)

- Fully supported by the Adept SDK, allowing custom JTAG/SPI applications to be created

**Works with all Xilinx tools – Fully supported by Digilent’s Adept software and Adept SDK

**Reference Manual